NANO编辑优选:基于阈值开关忆阻器的一体化安全硬件为物联网安全保驾护航

文章介绍

Guobin Zhang(张国滨), Jianhao Kan(阚建豪), Xuemeng Fan(凡雪蒙), Qi Luo(罗琪), Jiabao Sun(孙家宝), Dawei Gao(高大为) and Yishu Zhang(张亦舒)

通讯作者:

- 张亦舒,浙江大学集成电路学院

研究背景:

随着大数据和物联网时代的到来,物联网设备通常计算资源和存储容量有限,却需要处理和传输大量敏感数据,因此开发先进的物联网安全硬件至关重要。物理不可克隆函数(PUF)和真随机数生成器(TRNG)作为主流硬件安全原语,分别用于生成不可复制的认证凭证和真正的随机数,以确保系统的安全性和不可预测性。然而,现有的PUF和TRNG模块通常需要额外的电路开销,限制了其在物联网边缘设备中的大规模应用。本研究旨在通过基于阈值开关忆阻器的1T1R阵列,实现PUF和TRNG功能的统一集成,解决现有安全硬件在集成密度和能效方面的挑战,为物联网设备提供高效、可靠的安全解决方案。

研究方法:

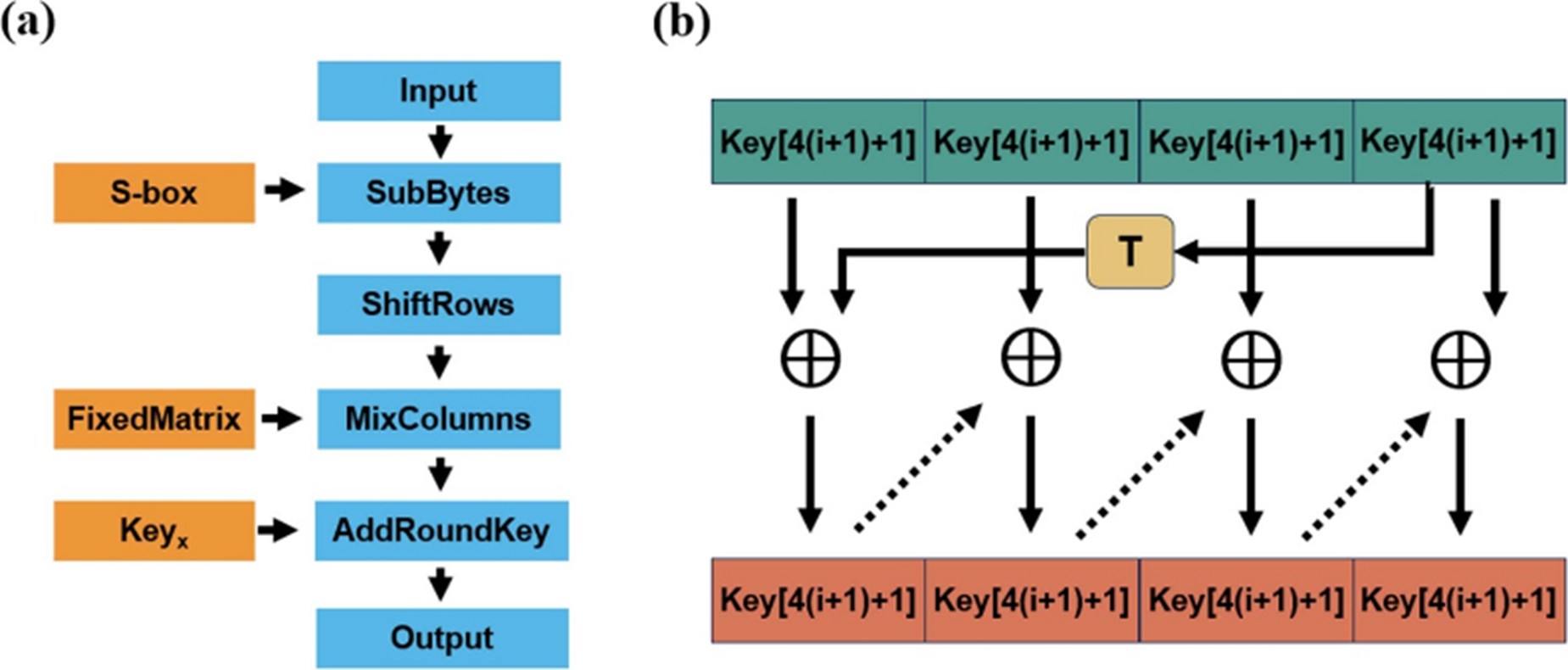

本研究通过构建32×32的1T1R阵列,基于阈值开关(TS)忆阻器成功实现了物理不可克隆函数(PUF)和真随机数生成器(TRNG)功能的统一集成。研究团队首先对FeOₓ薄膜的化学特性及TS忆阻器的电学性能进行了详细分析,验证了器件具有良好的循环稳定性和随机性(图1)。

图1薄膜的制造细节和化学特性。

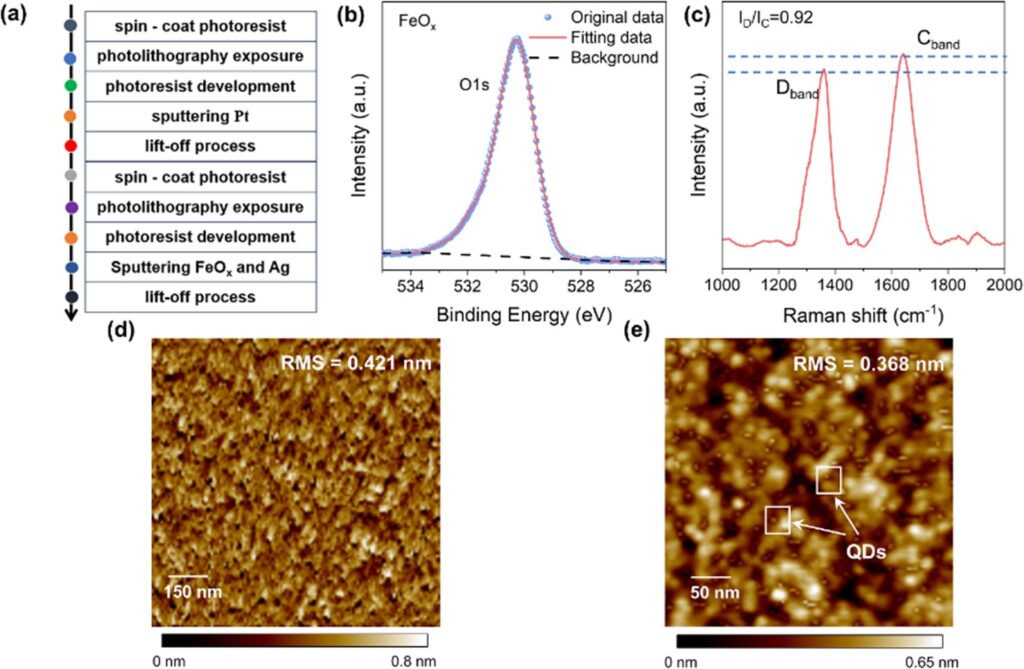

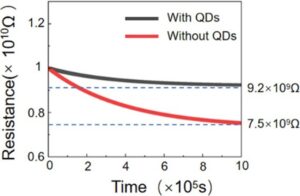

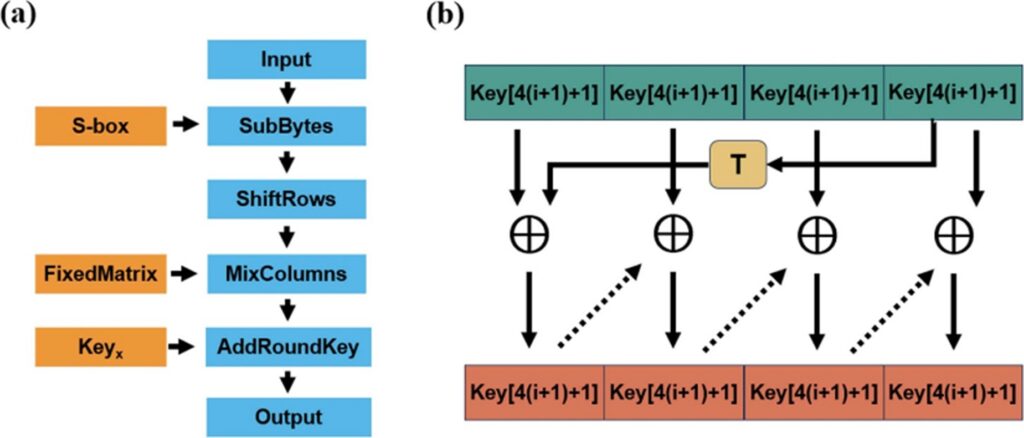

通过优化器件的材料和结构,研究实现了高可靠性忆阻器(图2)以及进一步的高均匀性和唯一性的PUF系统,其生成的PUF在均匀性、唯一性和鲁棒性方面表现出色,汉明重量接近理想值0.5,且在不同温度下的比特错误率(BER)保持在1.5%以下。此外,研究还基于CTR_DRBG算法成功部署了TRNG,生成的随机数通过了NIST-900测试,展现出卓越的随机性(图3)。实验结果表明,该设计的每比特能耗仅为0.043 pJ,随机数生成速率达到1621 Mbps,与同类工作相比,能耗降低了30%以上,生成速率提高了20%以上。这一成果不仅展示了TS忆阻器在硬件安全领域的应用潜力,还为解决物联网设备安全硬件的集成和能效问题提供了创新解决方案,显著提升了物联网设备的安全性和能效表现。

图2 TS忆阻器的数据保持能力(高阻态)

图3 (a) AES 128 的流程图。(b) 密钥生成示意图。

作者介绍

张亦舒 研究员

浙江大学

- 张亦舒,浙江大学求是科创学者, 浙江省海外高层次人才,浙江省集成电路创新平台兼聘研究员。主要从事忆阻器、存算一体和加密芯片、神经形态计算和集成电路工艺开发。他于 2019 年获得新加坡科技设计大学博士学位。发表论文50余篇,以一作和通讯作者发表包括Nature Communications, Advanced Materials (4篇),Advanced Functional Materials , ACS Nano和Nano Letters (5篇)等领域顶尖论文30余篇,拥有多项发明专利,主持国家和省级多项基金,担任多个国际学术期刊的青年编委。获得包括第二届全国博士后创新创业大赛银奖和HICOOL 2024全球创业大赛三等奖等奖项。

期刊介绍

- 2023年影响因子:2.9 Citescore:7.1

- Nanotechnology(NANO)创刊于1990年,是第一本纳米科研和技术领域的专业期刊。NANO发表纳米技术研究发展前沿的高水平研究论文及纳米研究进展的综述,主要集中在纳米能源、生物和医学、电子和光子、图案和纳米加工、传感和驱动、材料合成和材料性能等领域。